These html pages are based on the

PhD thesis "Cluster-Based Parallelization of Simulations on Dynamically Adaptive Grids and Dynamic Resource Management" by Martin Schreiber.

There is also

more information and a PDF version available.

7.1 Inavsive hardware architecture

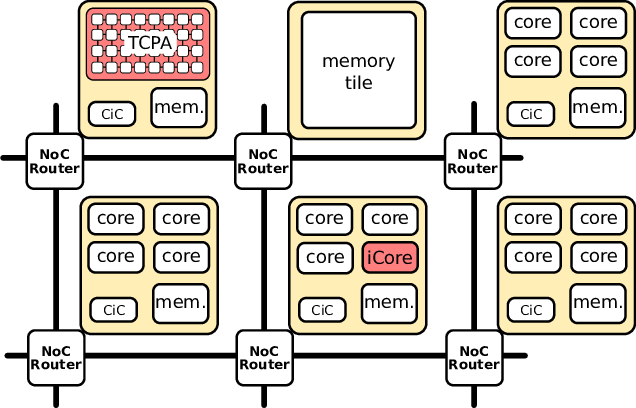

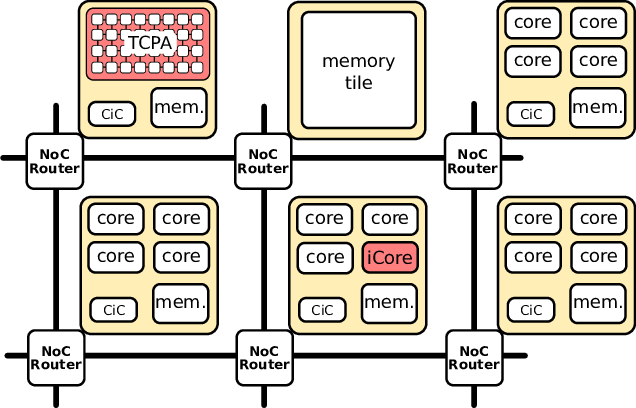

Here we give a short overview of the Invasive System architecture from the HPC perspective. An

example configuration of the Invasive Chip is given in Fig. 7.1.

- Network on Chip:

The hardware architecture is build upon a multi-tile infrastructure. The network on chip

(NoC) connects all tiles with a two-dimensional mesh network.

- Tile:

Each tile can have a local memory, a CiC, standard Leon cores and special accelerator

cores.

- CiC:

Programs are able to start computations on the same or on another tile. They enqueue

the kernels in the Core i-let Controller (CiC) of the target tile. The CiC is then able to

start the execution of kernels (i-lets) on the cores without software scheduling overheads.

- Accelerators:

Besides standard Leon cores, two different types of cores are available with the Invasive

system: On the one hand, tightly-coupled processor arrays (TCPAs) which are based on

a regular mesh of cores. The resources used by an existing programs can be extended by

infecting processing elements in their proximity or shrunk by retreating from processing

elements. On the other hand, i-Cores provide a run-time adaptive instruction set and

adaptive micro architecture. This allows uploading of special instructions and modification

of the core parameters to support applications which have different requirements.

- Memory model:

Each tile has a local memory with cache-coherent access on each tile. The global memory

on the memory tile is segmented and each segment is assigned to a single tile. For the

global-memory model and the the vision of thousands of invadable cores on one System

on Chip (SoC) making a cache coherency very challenging, we decided to use no cache

coherency between tiles.